| Multiport TSN Ethernet Swtich (MTSN)

10M/100M/1G Multiport TSN Ethernet Switch IP Core |

|

Overview

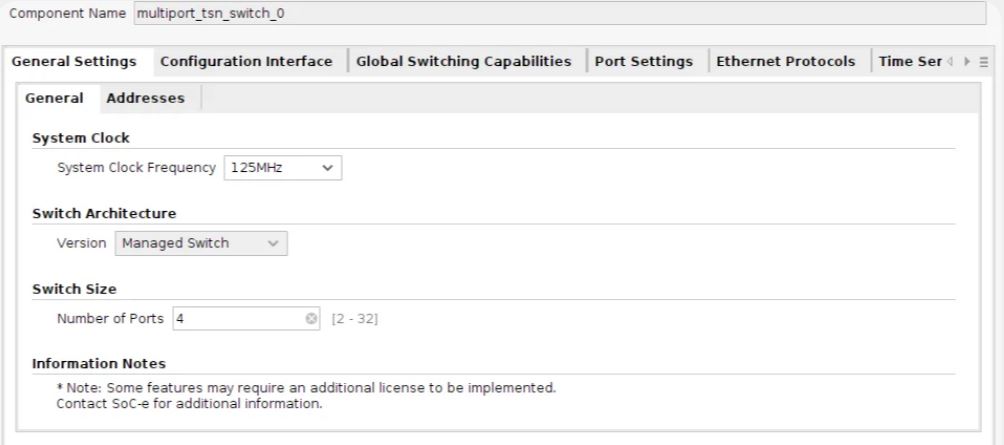

MTSN is a multi-port, multi-rate managed Ethernet switch with Time-Sensitive Networking (TSN) capabilities to achieve deterministic Ethernet solutions in which streams are delivered with guaranteed bandwidth and deterministic latency.

With a rich set of layer-2 configurable features, both at synthesis time & during runtime, MTSN allows building advanced Ethernet switch systems with TSN capabilities. MTSN switch has been designed to address the maximum throughput using optimized resources.

All these characteristics enable a wide number of applications/sectors where the use of MTSN IP Core is key. Automotive, Marine, Aerospace, Defence or Electric are examples of markets where our customers are already applying this technology.

Key Features

|

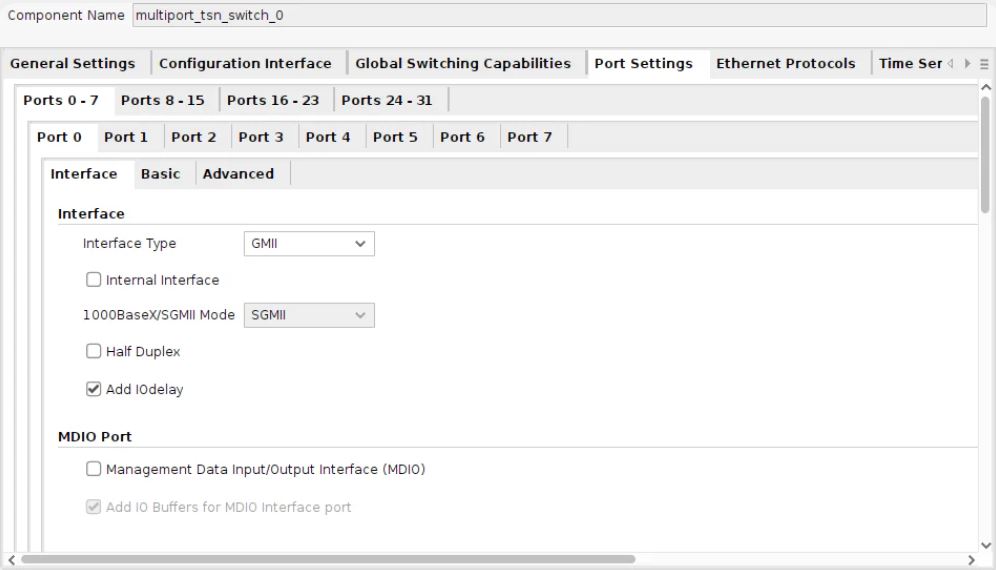

1. Time-Sensitive Networking (TSN) support Aligned with TSN profiles such as Aerospace (P802.1DP), Automotive (P802.1DG), Industrial Automation (IEC/IEEE 60802). 2. Ethernet Switch IP “builder” Hundreds of configurable parameters to build exact switch configuration, ensuring efficient use of logic resources. 3. Different Data-Rate Per Port Each port’s speed and interface can be assigned independently. |

4. High Performance Up to 1G interfaces without HOL (Head-of-Line) blocking. 5. Fast & Smooth Integration GUI support for AMD Vivado™, drivers & software components included. 6. Evaluation Version Available Encrypted, time-limited version available. |

Technical Specifications

Communication Interface

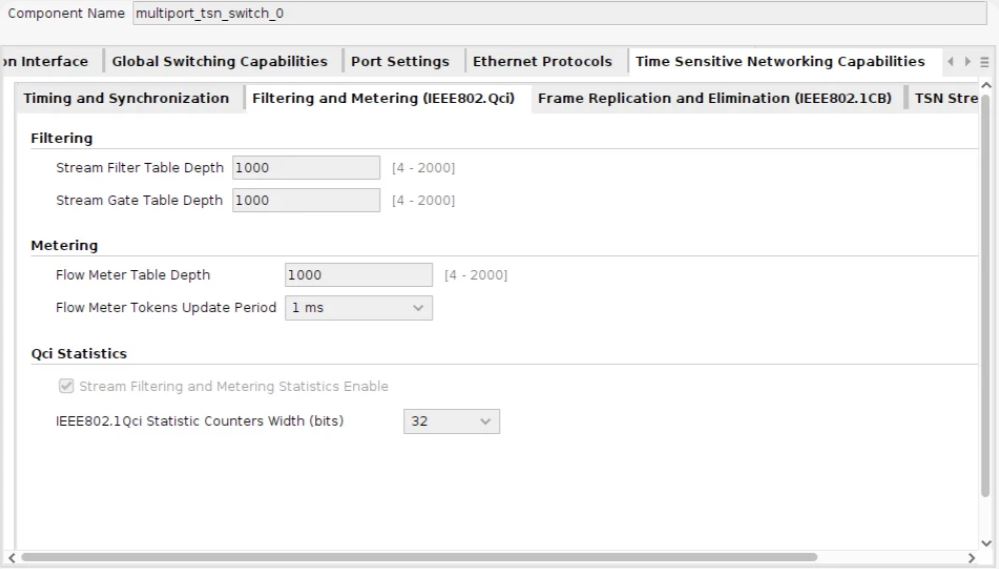

Time Sensitive Networking (TSN)

Time Synchronization

Traffic Management

|

Quality of Service

Network Management & Monitoring

Others

|

Technical Support, Verification & Deliverables

Technical Support: direct access to experienced support engineers during development and integration phases.

Verification: block simulation, global simulation, in-hardware validation.

Deliverables:

- Encrypted/Source RTL code

- Drivers, API, SW stacks

- Documentation

- (Optional) Networking Testbench Suite (NTS)

- (Optional) Vivado™ example design

Evaluation & Design-in Kit

Evaluate MTSN via RelyUm Industrial TSN Switches and Endpoints: See details

DOWNLOAD: MTSN Brochure

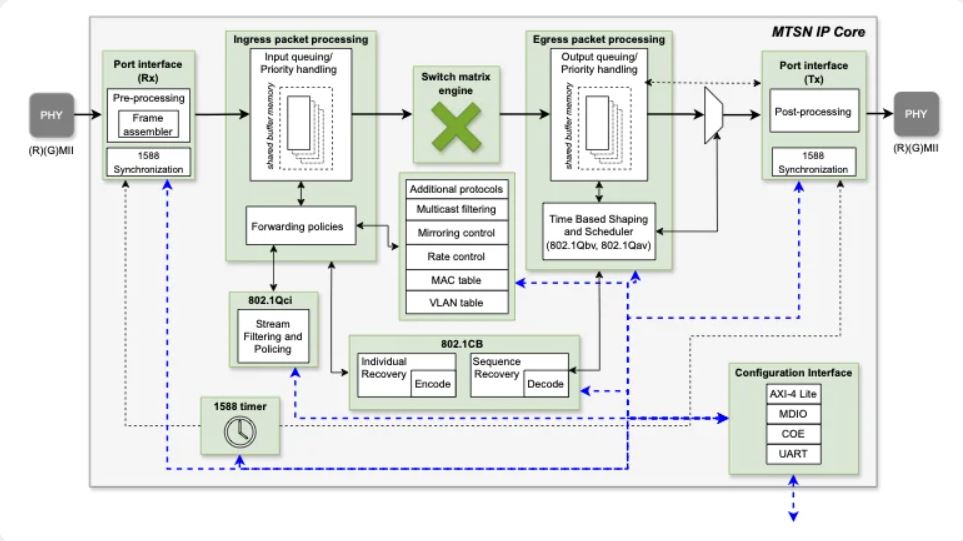

Diagrams

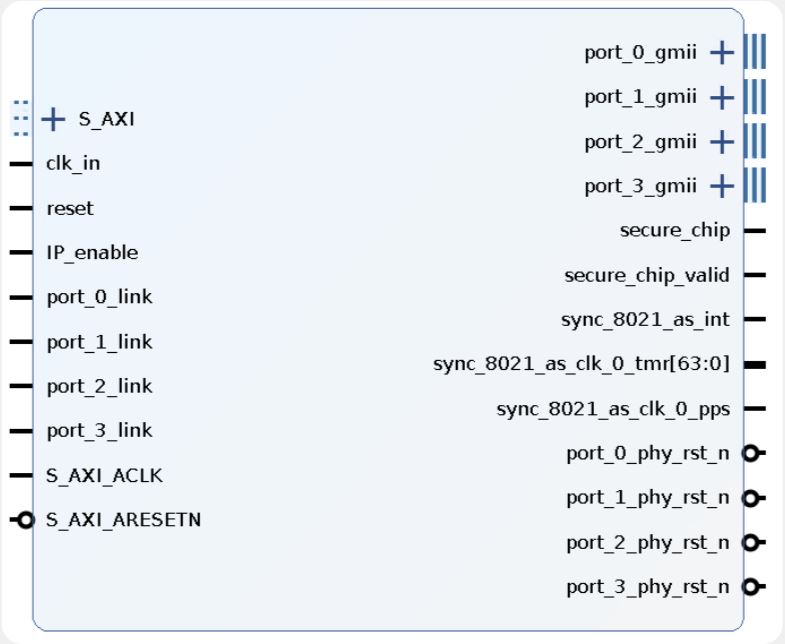

MTSN-1G TSN Ethernet Switch

MTSN-1G TSN Ethernet Switch