UES Switch Core

|

|

Overview

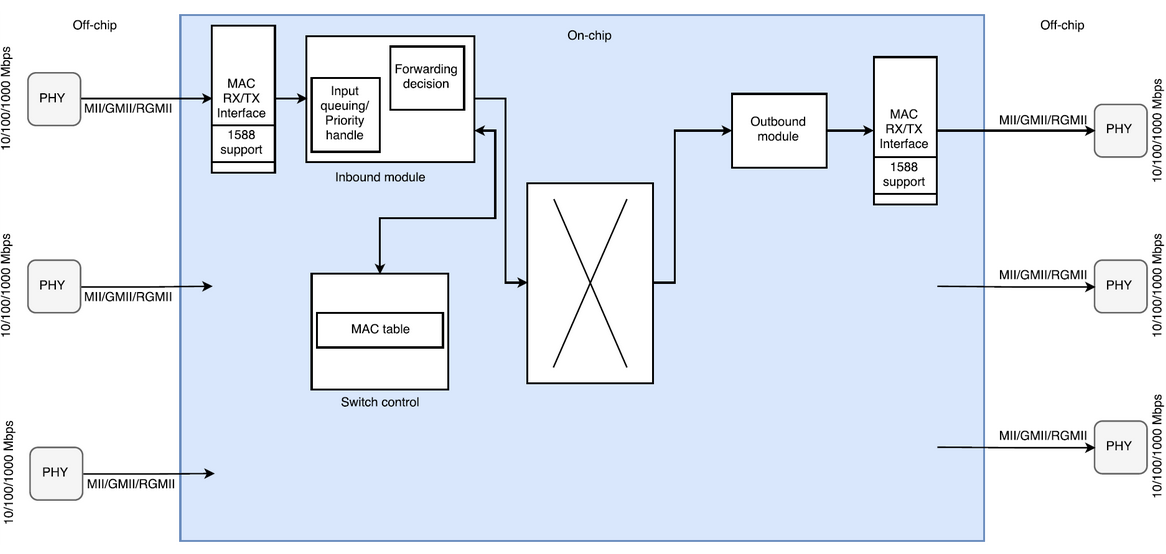

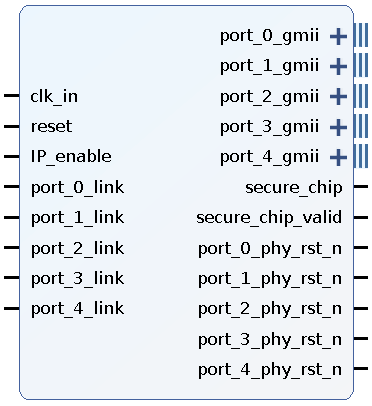

The Unmanaged Ethernet Switch IP core (UES) implements a plug-and-play Ethernet switch on reconfigurable devices. It does not require external configuration. It has been designed to address the maximum throughput using the minimum resources.

The switch implements a non-blocking crossbar matrix that allows wire-speed communication among all the ports. The switch buffers and verifies each frame before forwarding it. nevertheless, the latency time has been minimized to an order of nanoseconds. Furthermore, UES supports IEEE 1588 V2 Transparent Clock functionalities. This feature, which corrects PTP frames introducing the error that the switch generates, allows the interconnection of IEEE 1588 synchronized devices maintaining the highest levels of accuracy.

UES is the perfect Ethernet Switch IP to implement Ethernet based Industrial Networks. It provides MII/GMII/RGMII native interfaces fo Ethernet PHY devices and it can be combined with Xilinx IP to support RMII or SGMII among other interfaces. It also supports the AXI4-Stream interface, to be connected to other IP Cores that do not feature MAC based interfaces.

Key Features

- Plug-and-Play: no configuration required

- High performance: Full-crossbar matrix among ports implemented to allow maximum throughput

- Fast: Very reduced Latency Times thanks to a SoC-e address matching mechanism

- Efficient: Optimized to require few logic resources in order to allow the implementation of low-cost FPGA devices

- Flexible: Fully scalable and configurable to obtain the best functionalities-size trade-off. The following parameters are available for the designer:

- Number of ports: Configurable from 3 to 16 Ethernet ports

- Buffers queue length

- IEEE Transparent Clock functionalities

- Automatic: MAC addresses learning and aging (by default, store capacity of 2048 MAC addresses).

|

Supported FPGAs

- 6-Series (Spartan, Virtex)

- 7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

- Ultrascale (Kintex, Virtex)

- Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

Embedded Development Suite

A hardware development platform is available. Latest documentation, design support files, reference design source files and tools are available for download free of charge.

* Device supported by the free Xilinx Vivado WebPACK tool.

Pricing, Availability and Ordering

- Concurrent EDA is the US Distributor for SoC-e.

- Currently Available to US customers only.

- Please email Ray at

This email address is being protected from spambots. You need JavaScript enabled to view it. with questions / quotes / orders.