Multiport TSN Switch (MTSN)10M/100M/1G Multiport TSN Ethernet Switch IP Core |

|

OVERVIEW

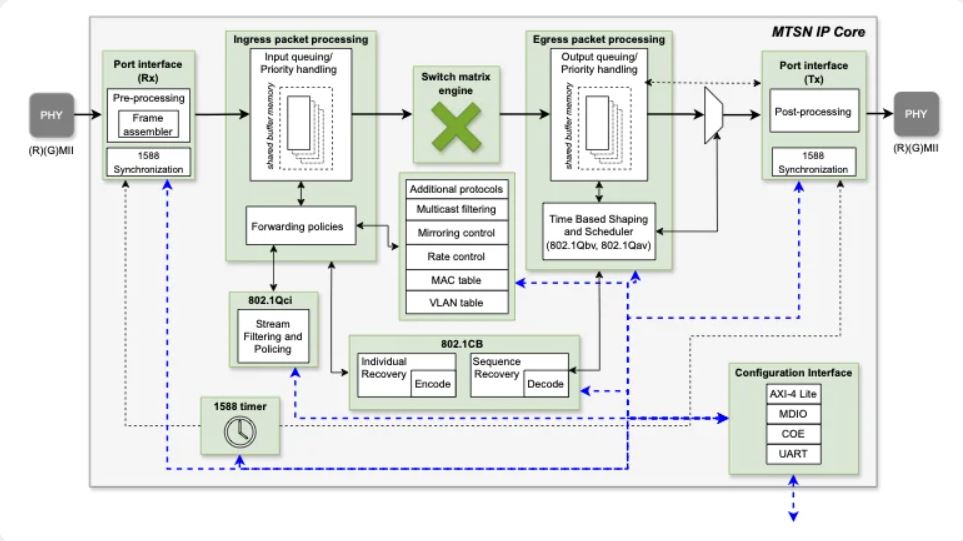

MTSN is a multi-port, multi-rate managed Ethernet switch with Time-Sensitive Networking (TSN) capabilities that delivers guaranteed bandwidth and deterministic latency.

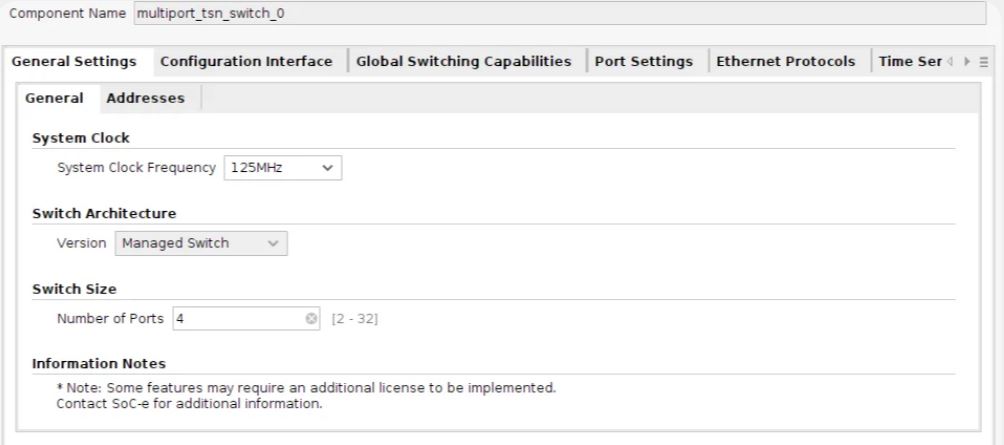

With a rich set of layer-2 configurable features, both at synthesis time & during runtime, MTSN allows building advanced Ethernet switch systems with TSN capabilities. MTSN switch has been designed to address the maximum throughput using optimized resources.

All these characteristics enable a wide number of applications/sectors where the use of MTSN IP Core is key. Automotive, Marine, Aerospace, Defence or Electric are examples of markets where our customers are already applying this technology.

KEY FEATURES

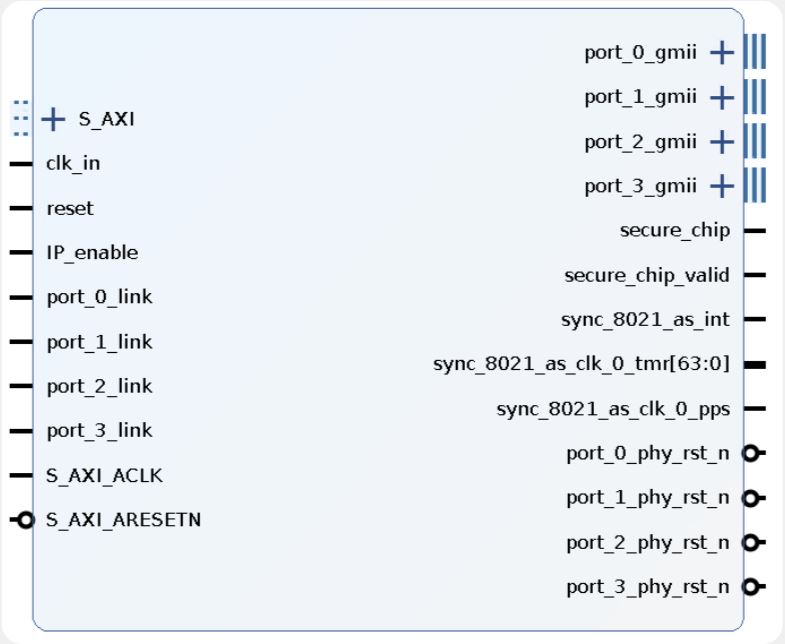

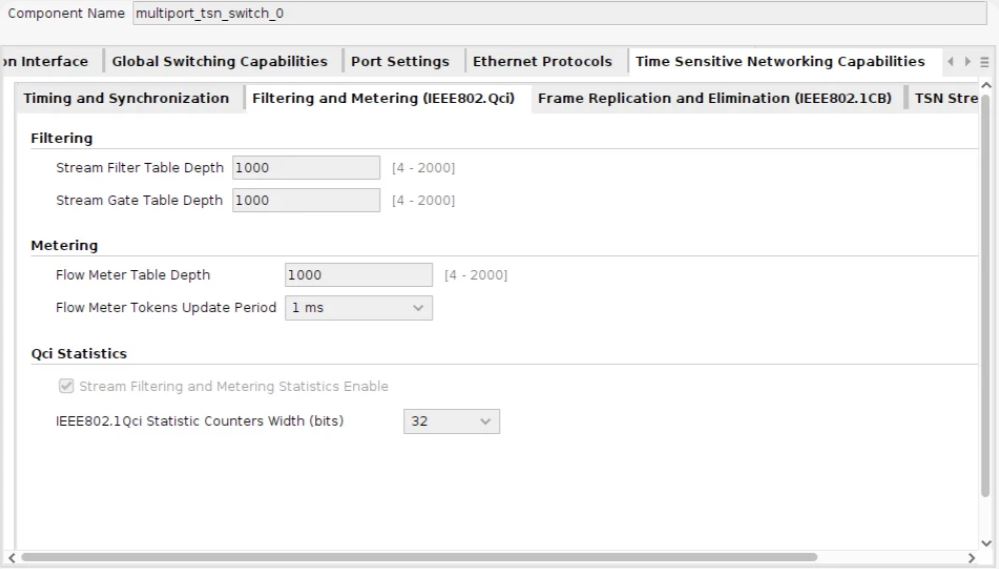

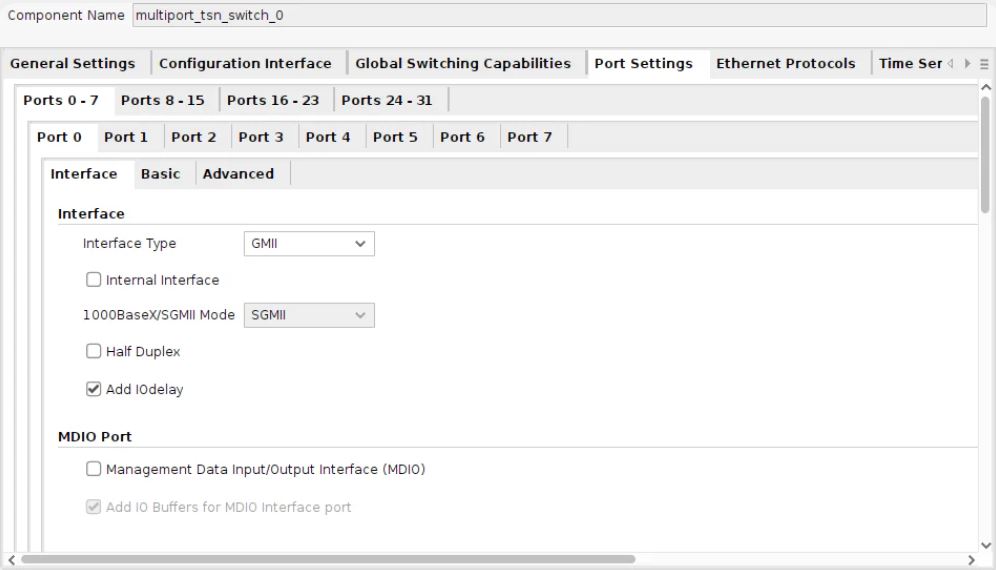

1. Time-Sensitive Networking (TSN) supportAligned with the different TSN profiles, such as Aerospace (P802.1DP), Automotive (P802.1DG) or Industrial Automation (IEC/IEEE 60802). 2. Ethernet Switch IP “builder”Hundreds of user-configurable parameters allow obtaining the exact switch configuration required by the customer, ensuring efficient use of the available programmable logic resources. 3. Different Data-Rate Per PortEach port speed and interface can be assigned independently. |

4. High PerformanceUp-to 1G interfaces without HOL (Head-of-line) blocking effect. 5. Fast & Smooth IntegrationGUI available for some FPGA vendor tools (i.e., AMD Vivado™ Design Suite). Drivers & software components included as part of the product deliverable. 6. Evaluation Version AvailableEncrypted, time-limited version available. |

Technical Specifications

Communication Interface

Time Sensitive Networking (TSN)

Time Synchronization

Traffic Management

|

Quality of Service

Network Management & Monitoring

Others

|

Technical Support, Verification & Deliverables

Technical Support

IP Licenses are provided along with a Technical Support package that ensures a direct communication channel with our highly experienced support engineers. This is vastly valued during customer product development & integration phases.

Verification

All our IP Cores are rigorously tested, hardware-validated and verified in real-life environments. A 3-phase IP product verification is applied:

- Entity/Block-oriented simulation

- Global-oriented simulation

- In-hardware validation

Deliverables

- Encrypted/Source RTL code

- Software components: Drivers, configuration API & SW stacks

- Documentation (IP Core and Software components)

- (Optional) Networking Testbench Suite (NTS)

- (Optional) AMD Vivado™ design suite example design

Evaluation & Design-in Kit

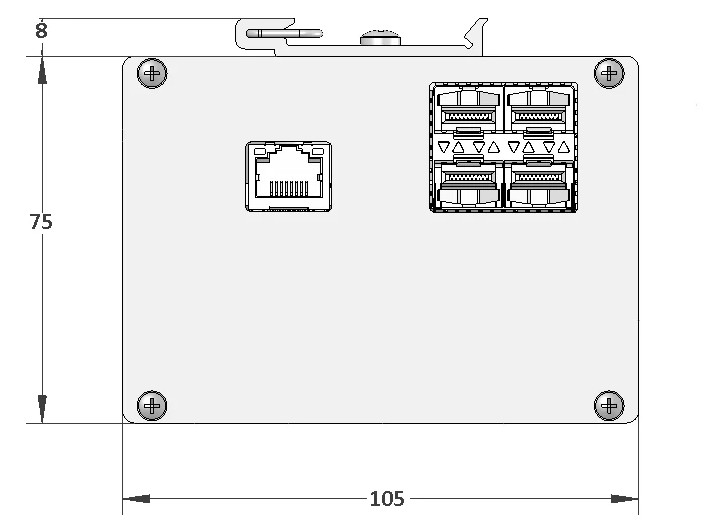

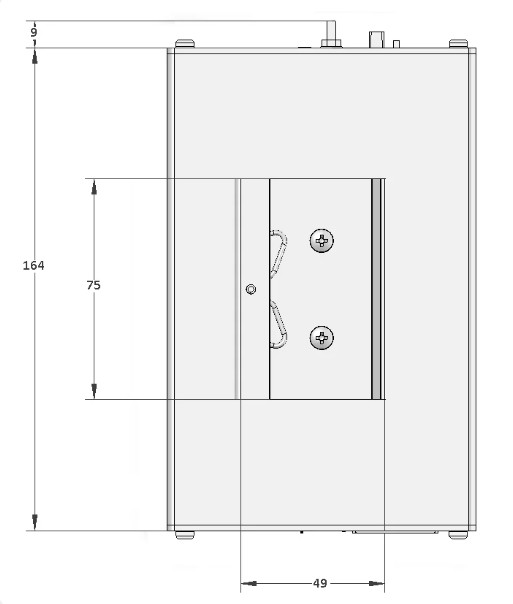

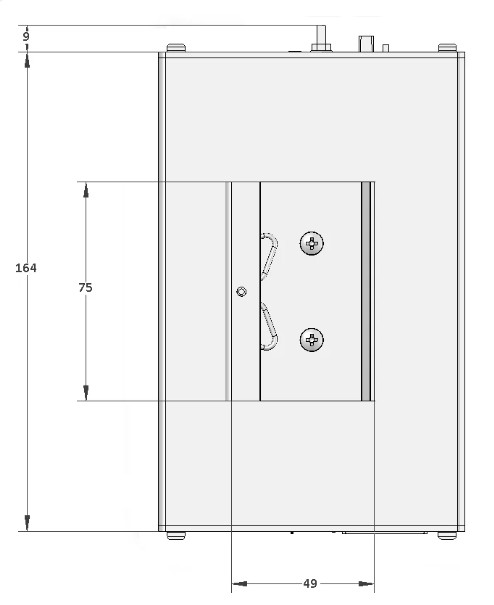

To evaluate MTSN in a plug & play platform, see the RelyUm Industrial TSN Switches and Endpoints family:

https://soc-e.com/relyum-industrial/tsn-switches-and-endpoint-switches/

DOWNLOAD: MTSN Brochure