Open Instrument Platform: Red Pitaya

Overview

Red Pitaya is an open-source measurement and control tool replacing many expensive laboratory instruments!

Key Features

- High performance hardware at a surprising price tag.

- Replaces most essential instruments:

- Oscilloscope

- Spectrum Analyzer

- Signal Generator, LCR meter)

- LAN or wireless access from any WEB browser via tablet or a PC regardless of the OS (MAC, Linux, Windows, Android, iOS).

- LabView and MATLAB® interface.

- Possibility to make your own application and share it with others.

- Open source software.

Software

Red Pitaya is based on GNU/Linux operating system and can be customized at different programming levels. Available software interfaces include: HDL, C/C++, scripting languages, MATLAB and HTML based web interfaces.

A hardware development platform is available. Latest documentation, design support files, reference design source files and tools are available for download free of charge.

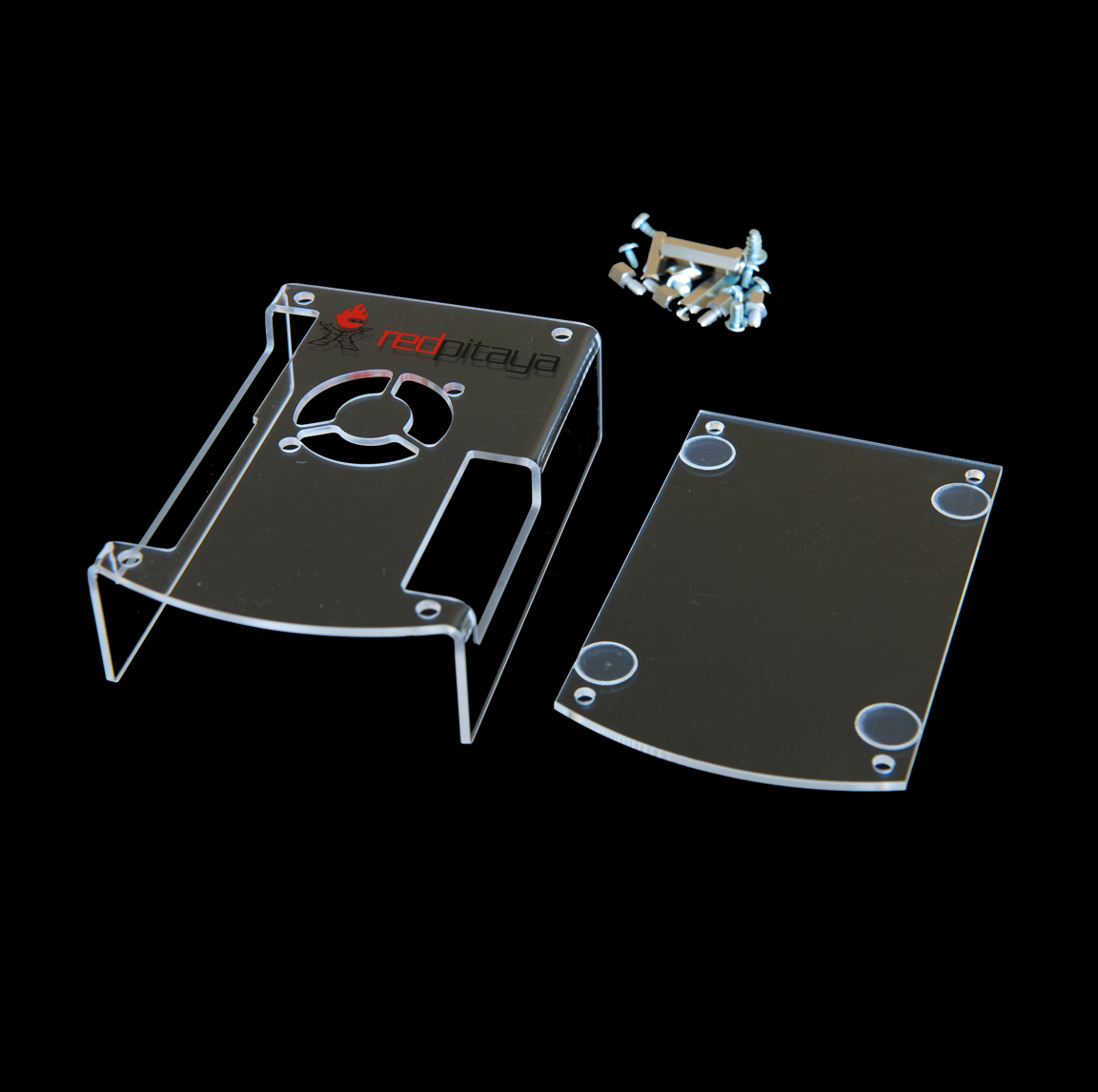

Red Pitaya Diagnostic Kit with Enclosure

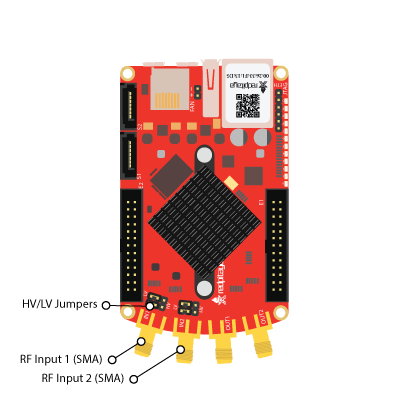

- 1x Red PItaya (v1.1)

- 2x Pintex CP-2100 Oscilloscope Probes

- 2x SMA to BNC Adapters to attach probes

- 1x Micro USB Power Supply Adapater

- 4GB Micro SD Card

- Transparent Enclosure

|

|

||

|

|

|

|

Pricing and Availability

- Pricing: $325

- Availability: Now

- Ships from United States

- Call 412-687-8800